|

Ciekawostki o 8-bitowych mikrokontrolerach AVR |  |

ATtiny85 (20PU) |  ATmega48 (20PU) |  ATmega32A (PU) |

| DDXn (DDRX) | PORTXn (PORTX) | PUD (MCUCR) | Konfiguracja pinu PXn |

| 0 | 0 | X | IN Z |

| 0 | 1 | 0 | IN H (pu) |

| 0 | 1 | 1 | IN Z |

| 1 | 0 | X | OUT L |

| 1 | 1 | X | OUT H |

| Początkowa konfiguracja pinu PXn [DDXn:PORTXn] | Docelowa konfiguracja pinu PXn [DDXn:PORTXn] | |||

| IN Z [0:0] | IN H (pu) [0:1] | OUT L [1:0] | OUT H [1:1] | |

| IN Z [0:0] | - | IN H (pu) [0:1] | OUT L [1:0] | IN H (pu) [0:1] OUT H [1:1] OUT L [1:0] OUT H [1:1] |

| IN H (pu) [0:1] | IN Z [0:0] | - | OUT H [1:1] OUT L [1:0] IN Z [0:0] OUT L [1:0] | OUT H [1:1] |

| OUT L [1:0] | IN Z [0:0] | OUT H [1:1] IN H (pu) [0:1] IN Z [0:0] IN H (pu) [0:1] | - | OUT H [1:1] |

| OUT H [1:1] | IN H (pu) [0:1] IN Z [0:0] OUT L [1:0] IN Z [0:0] | IN H (pu) [0:1] | OUT L [1:0] | - |

| Aby wyłączyć timer WDT (Watch-Dog Timer), należy ustawić wartość fuse bitu WDTON na "1" oraz zapi- sać "0" do bitów: WDRF w rejestrze MCUSR (Micro- Controller Unit Status Register), WDE i WDIE w re- jestrze WDTCR (WatchDog Timer Control Register) - według procedury opisanej w nocie katalogowej. Domyślnie timer WDT jest wyłączony po włączeniu/ resecie fabrycznie nowego mikrokontrolera. Aby wyłączyć moduł monitorowania napięcia zasi- lania BOD (Brown-Out Detector), należy ustawić wartość fuse bitów BODLEVEL2-0 na "1". Domyślnie moduł ten jest wyłączony w fabrycznie nowym mikrokontrolerze. Aby wyłączyć moduł debugowania dW (debugWire), należy ustawić wartość fuse bitu DWEN na "1". Domyślnie moduł ten jest wyłączony w fabrycznie nowym mikrokontrolerze. Aby wyłączyć przetwornik analogowo-cyfrowy ADC (Analog to Digital Converter), należy zapisać "0" do bitu ADEN w rejestrze ADCSRA (ADC control and Status Register A) - spowoduje to całkowite odłą- czenie jego napięcia zasilania. Dopiero później |

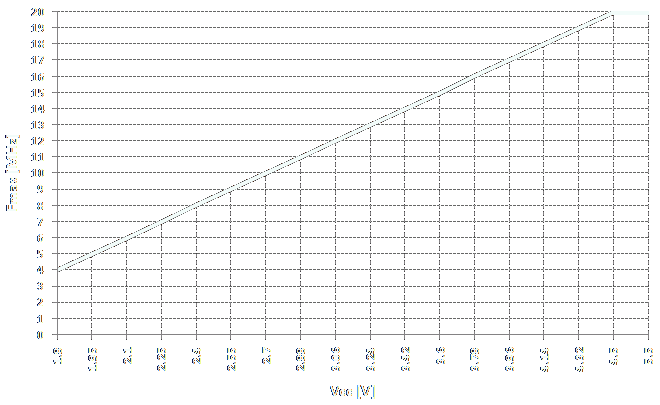

| Przykładowo w moim ATtiny85 zasilanym napięciem Vcc=5.0V, prąd płynący między podciągniętym pinem PB0, a masą zasilania wynosił 0.138mA. Stąd, po obliczeniach: Rpu = 5V / 0.000138A = 36231.88 omów. Wartości wewnętrznych rezystorów mogą być inne w różnych egzem- plarzach tego samego modelu mikrokontrolera, ale są bardzo zbliżone do siebie na różnych pinach jednego układu. Rezystory te są prawdo- podobnie wykonane na krzemie, jako tranzystory FET z długim cienkim kanałem. Zajmują mniej miejsca, są łatwiejsze i tańsze w produkcji niż tradycyjne rezystory, ale mają gorszą liniowość i stabilność tempera- turową. |

| Podanie napięcia Vin o wartości wyższej niż Vcc+0.5V, spowoduje przepływ prądu przez górną diodę zabezpieczającą Dup do plusa zasilania, a w re- zultacie zmniejszenie napięcia Vin do wartości Vcc+0.5V. Z kolei podanie napięcia Vin o wartości niższej niż GND-0.5V, spowoduje przepływ prądu przez dolną diodę zabezpieczającą Ddn do masy zasilania, a w rezultacie zmniejszenie napięcia Vin do wartości GND-0.5V. Jedynym ograniczeniem jest zalecany maksymalny prąd płynący przez wew- nętrzne diody zabezpieczające, który nie powinien przekroczyć wartości 1mA. Większy prąd może spowodować uszkodzenie diody zabezpieczającej, a następnie pinu/portu mikrokontrolera. Wynika z tego, że stosując odpowiednio dużą wartość rezystancji wejściowej Rin, na pin mikrokontrolera można podać napięcie wejściowe Vin, o wartości znacznie przekraczającej jego maksymalny zakres podany w nocie katalogo- wej (od GND-0.5V do Vcc+0.5V). Przy rezystorze Rin=1M na pin mikrokontrolera można podać napięcie uje- |

| Model | FLASH/EEPR- OM/SRAM [B] | Sygnatura | Fmax [MHz] | Vcc [V] | Interfejs | Obudowa |

| AT90 | ||||||

| AT90S1200-4 AT90S1200-12 | 1k/64/- | 1E9001* | 4 12 | 2.7-6.0 4.0-6.0 | ISP/HVPP | DIP20/SOIC20/SSOP20 |

| AT90S2313-4 AT90S2313-10 | 2k/128/128 | 1E9101* | 4 10 | 2.7-6.0 4.0-6.0 | ISP/HVPP | DIP20/SOIC20 |

| AT90S2323-10 AT90LS2323-4 | 2k/128/128 | 1E9102* | 10 4 | 4.0-6.0 2.7-6.0 | ISP/HVSP | DIP8/SOIC8 |

| AT90S2333-8 AT90LS2333-4 | 2k/128/128 | 1E9105* | 8 4 | 4.0-6.0 2.7-6.0 | ISP/HVPP | DIP28/TQFP32 |

| AT90S2343-10 AT90LS2343-4 AT90LS2343-1 | 2k/128/128 | 1E9103* | 10 4 1 | 4.0-6.0 2.7-6.0 2.7-6.0 | ISP/HVSP | DIP8/SOIC8 |

| AT90S4414-4 AT90S4414-8 | 4k/256/256 | 1E9201* | 4 8 | 2.7-6.0 4.0-6.0 | ISP/HVPP | DIP40/PLCC44/TQFP44 |

| AT90S4433-8 AT90LS4433-4 | 4k/256/128 | 1E9203* | 8 4 | 4.0-6.0 2.7-6.0 | ISP/HVPP | DIP28/TQFP32 |

| AT90S4434-8 AT90LS4434-4 | 4k/256/256 | 1E9202* | 8 4 | 4.0-6.0 2.7-6.0 | ISP/HVPP | DIP40/PLCC44/TQFP44 |

| AT90S8515-4 AT90S8515-8 | 8k/512/512 | 1E9301* | 4 8 | 2.7-6.0 4.0-6.0 | ISP/HVPP | DIP40/PLCC44/TQFP44 |

| AT90C8534 AT90VC8534 | 8k/512/256 | 1E9304 | 1.5 1 | 3.3-6.0 | LVPP | TQFP48 |

| AT90S8535-8 AT90LS8535-4 | 8k/512/512 | 1E9303* | 8 4 | 4.0-6.0 2.7-6.0 | ISP/HVPP | DIP40/PLCC44/TQFP44 |

| AT90CAN32 | 32k/1k/2k | 1E9581 | 16 | 2.7-5.5 | ISP/HVPP/JTAG | TQFP64/VQFN64 |

| AT90CAN64 | 64k/2k/4k | 1E9681 | 16 | 2.7-5.5 | ISP/HVPP/JTAG | TQFP64/VQFN64 |

| AT90CAN128 | 128k/4k/4k | 1E9781 | 16 | 2.7-5.5 | ISP/HVPP/JTAG | TQFP64/VQFN64 |

| AT90PWM1 | 8k/512/512 | 1E9383 | 16 | 2.7-5.5 | ISP/HVPP/dW | SOIC24/VQFN32 |

| AT90PWM2 AT90PWM2B | 8k/512/512 | 1E9381 1E9383 | 16 | 2.7-5.5 | ISP/HVPP/dW | SOIC24 |

| AT90PWM3 AT90PWM3B | 8k/512/512 | 1E9381 1E9383 | 16 | 2.7-5.5 | ISP/HVPP/dW | SOIC32/VQFN32 |

| AT90PWM81 | 8k/512/256 | 1E9388 | 16 | 2.7-5.5 | ISP/HVPP/dW | SOIC20/VQFN32 |

| AT90PWM161 | 16k/512/1k | 1E948B | 16 | 2.7-5.5 | ISP/HVPP/dW | SOIC20/VQFN32 |

| AT90PWM216 AT90PWM316 | 16k/512/1k | 1E9483 | 16 | 2.7-5.5 | ISP/HVPP/dW | SOIC24 SOIC32/VQFN32 |

| AT90USB82 | 8k/512/512 | 1E9382 | 16 | 2.7-5.5 | ISP/HVPP/dW | VQFN32 |

| AT90USB162 | 16k/512/512 | 1E9482 | 16 | 2.7-5.5 | ISP/HVPP/dW | TQFP32/VQFN32 |

| AT90USB646 AT90USB647 | 64k/2k/4k | 1E9682 | 16 | 2.7-5.5 | ISP/HVPP/JTAG | TQFP64/VQFN64 |

| AT90USB1286 AT90USB1287 | 128k/4k/8k | 1E9782 | 16 | 2.7-5.5 | ISP/HVPP/JTAG | TQFP64/VQFN64 |

| ATtiny | ||||||

| ATtiny4 | 512/-/32 | 1E8F0A | 12 | 1.8-5.5 | TPI | SOT23-6/UDFN8 |

| ATtiny5 | 512/-/32 | 1E8F09 | 12 | 1.8-5.5 | TPI | SOT23-6/UDFN8 |

| ATtiny9 | 1k/-/32 | 1E9008 | 12 | 1.8-5.5 | TPI | SOT23-6/UDFN8 |

| ATtiny10 | 1k/-/32 | 1E9003 | 12 | 1.8-5.5 | TPI | SOT23-6/UDFN8 |

| ATtiny11 ATtiny11L | 1k/-/- | 1E9004 | 6 2 | 4.0-5.5 2.7-5.5 | HVSP | DIP8/SOIC8 |

| ATtiny12 ATtiny12L ATtiny12V | 1k/64/- | 1E9005* | 8 4 1.2 | 4.0-5.5 2.7-5.5 1.8-5.5 | ISP/HVSP | DIP8/SOIC8 |

| ATtiny13 ATtiny13A ATtiny13V | 1k/64/64 | 1E9007 | 20 20 10 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVSP/dW | DIP8/SOIC8/VDFN10/WQFN20 |

| ATtiny15L | 1k/64/- | 1E9006 | 1.6 | 2.7-5.5 | ISP/HVSP | DIP8/SOIC8 |

| ATtiny20 | 2k/-/128 | 1E910F | 12 | 1.8-5.5 | TPI | SOIC14/TSSOP14/VQFN20/ UFBGA15/WLCSP12 |

| ATtiny22 ATtiny22L | 2k/128/128 | 1E9106* | 8 4 | 4.0-6.0 2.7-6.0 | ISP/HVSP | DIP8/SOIC8 |

| ATtiny24 ATtiny24A ATtiny24V | 2k/128/128 | 1E910B | 20 20 10 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVSP/dW | DIP14/SOIC14/WQFN20 DIP14/SOIC14/VQFN20/WQFN20/UFBGA15 DIP14/SOIC14/WQFN20 |

| ATtiny25 ATtiny25V | 2k/128/128 | 1E9108 | 20 10 | 2.7-5.5 1.8-5.5 | ISP/HVSP/dW | DIP8/SOIC8/WQFN20 |

| ATtiny26 ATtiny26L | 2k/128/128 | 1E9109 | 16 8 | 4.5-5.5 2.7-5.5 | ISP/HVPP | DIP20/SOIC20/VQFN32 |

| ATtiny28L ATtiny28V | 2k/-/- | 1E9107 | 4 1.2 | 2.7-5.5 1.8-5.5 | HVPP | DIP28/TQFP32/VQFN32 |

| ATtiny40 | 4k/-/256 | 1E920E | 12 | 1.8-5.5 | TPI | SOIC20/TSSOP20/VQFN20 |

| ATtiny43U | 4k/64/256 | 1E920C | 8 | 1.8-5.5 | ISP/HVPP/dW | SOIC20/WQFN20 |

| ATtiny44 ATtiny44A ATtiny44V | 4k/256/256 | 1E9207 | 20 20 10 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVSP/dW | DIP14/SOIC14/WQFN20 DIP14/SOIC14/VQFN20/WQFN20/UFBGA15 DIP14/SOIC14/WQFN20 |

| ATtiny45 ATtiny45V | 4k/256/256 | 1E9206 | 20 10 | 2.7-5.5 1.8-5.5 | ISP/HVSP/dW | DIP8/SOIC8/TSSOP8/WQFN20 |

| ATtiny48 | 4k/64/256 | 1E9209 | 12 | 1.8-5.5 | ISP/HVPP/dW | DIP28/TQFP32/ VQFN28/VQFN32/UFBGA32 |

| ATtiny84 ATtiny84A ATtiny84V | 8k/512/512 | 1E930C | 20 20 10 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVSP/dW | DIP14/SOIC14/WQFN20 DIP14/SOIC14/VQFN20/WQFN20/UFBGA15 DIP14/SOIC14/WQFN20 |

| ATtiny85 ATtiny85V | 8k/512/512 | 1E930B | 20 10 | 2.7-5.5 1.8-5.5 | ISP/HVSP/dW | DIP8/SOIC8/WQFN20 |

| ATtiny87 | 8k/512/512 | 1E9387 | 16 | 1.8-5.5 | ISP/HVPP/dW | SOIC20/TSSOP20/VQFN32 |

| ATtiny88 | 8k/64/512 | 1E9311 | 12 | 1.8-5.5 | ISP/HVPP/dW | DIP28/TQFP32/ VQFN28/VQFN32/UFBGA32 |

| ATtiny167 | 16k/512/512 | 1E9487 | 16 | 1.8-5.5 | ISP/HVPP/dW | SOIC20/TSSOP20/VQFN32/WQFN20 |

| ATtiny261 ATtiny261A ATtiny261V | 2k/128/128 | 1E910C | 20 20 10 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/dW | DIP20/SOIC20/VQFN32 DIP20/SOIC20/TSSOP20/VQFN32 DIP20/SOIC20/VQFN32 |

| ATtiny327 | 32k/1k/2k | 1E---- | 16 | 2.7-5.5 | ISP/HVPP/dW | SOIC20/TSSOP20/VQFN32/WQFN20 |

| ATtiny441 | 4k/256/256 | 1E9215 | 16 | 1.7-5.5 | ISP/HVSP/dW | SOIC14/VQFN20/WQFN20 |

| ATtiny461 ATtiny461A ATtiny461V | 4k/256/256 | 1E9208 | 20 20 10 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/dW | DIP20/SOIC20/VQFN32 DIP20/SOIC20/TSSOP20/VQFN32 DIP20/SOIC20/VQFN32 |

| ATtiny828 | 8k/256/512 | 1E9314 | 20 | 1.7-5.5 | ISP/HVPP/dW | TQFP32/VQFN32 |

| ATtiny841 | 8k/512/512 | 1E9315 | 16 | 1.7-5.5 | ISP/HVSP/dW | SOIC14/VQFN20/WQFN20 |

| ATtiny861 ATtiny861A ATtiny861V | 8k/512/512 | 1E930D | 20 20 10 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/dW | DIP20/SOIC20/VQFN32 DIP20/SOIC20/TSSOP20/VQFN32 DIP20/SOIC20/VQFN32 |

| ATtiny1634 ATtiny1634R | 16k/256/1k | 1E9412 | 12 | 1.8-5.5 | ISP/HVPP/dW | SOIC20/WQFN20 |

| ATtiny2313 ATtiny2313A ATtiny2313V | 2k/128/128 | 1E910A | 20 20 10 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/dW | DIP20/SOIC20/WQFN20 DIP20/SOIC20/VQFN20/WQFN20 DIP20/SOIC20/WQFN20 |

| ATtiny4313 | 4k/256/256 | 1E920D | 20 | 1.8-5.5 | ISP/HVPP/dW | DIP20/SOIC20/VQFN20/WQFN20 |

| ATmega | ||||||

| ATmega4HVD | 4k/256/512 | 1E9313 | 4 | 2.1-5.5 | ISP/HVSP/dW | DRDFN18 |

| ATmega8 ATmega8A ATmega8L | 8k/512/1k | 1E9307 | 16 16 8 | 4.5-5.5 2.7-5.5 2.7-5.5 | ISP/HVPP | DIP28/TQFP32/VQFN32 DIP28/TQFP32/VQFN32 DIP28/TQFP32/VQFN32 |

| ATmega8U2 | 8k/512/512 | 1E9389 | 16 | 2.7-5.5 | ISP/HVPP/dW | TQFP32/VQFN32 |

| ATmega8HVA | 8k/256/512 | 1E9310 | 4 | 1.8-9.0 | ISP/HVSP/dW | TSOP28/LGA36 |

| ATmega8HVD | 8k/256/512 | 1E9312 | 4 | 2.1-5.5 | ISP/HVSP/dW | DRDFN18 |

| ATmega16 ATmega16A ATmega16L | 16k/512/1k | 1E9403 | 16 16 8 | 4.5-5.5 2.7-5.5 2.7-5.5 | ISP/HVPP/JTAG | DIP40/TQFP44/VQFN44 |

| ATmega16M1 | 16k/512/1k | 1E9484 | 16 | 2.7-5.5 | ISP/HVPP/dW | TQFP32/VQFN32 |

| ATmega16U2 | 16k/512/512 | 1E9489 | 16 | 2.7-5.5 | ISP/HVPP/dW | TQFP32/VQFN32 |

| ATmega16U4 ATmega16U4RC | 16k/512/1.25k | 1E9488 | 16 | 2.7-5.5 | ISP/HVPP/JTAG | TQFP44/VQFN44 |

| ATmega16HVA ATmega16HVA2 | 16k/256/512 16k/256/1k | 1E940C 1E940E | 4 | 1.8-9.0 | ISP/HVSP/dW | TSOP28/LGA36 |

| ATmega16HVB | 16k/512/1k | 1E940D | 8 | 4.0-18.0 | ISP/HVPP/dW | TSSOP44 |

| ATmega32 ATmega32A ATmega32L | 32k/1k/2k | 1E9502 | 16 16 8 | 4.5-5.5 2.7-5.5 2.7-5.5 | ISP/HVPP/JTAG | DIP40/TQFP44/VQFN44 |

| ATmega32C1 | 32k/1k/2k | 1E9586 | 16 | 2.7-5.5 | ISP/HVPP/dW | TQFP32/VQFN32 |

| ATmega32M1 | 32k/1k/2k | 1E9584 | 16 | 2.7-5.5 | ISP/HVPP/dW | TQFP32/VQFN32 |

| ATmega32U2 | 32k/1k/1k | 1E958A | 16 | 2.7-5.5 | ISP/HVPP/dW | TQFP32/VQFN32 |

| ATmega32U4 ATmega32U4RC | 32k/1k/2.5k | 1E9587 | 16 | 2.7-5.5 | ISP/HVPP/JTAG | TQFP44/VQFN44 |

| ATmega32U6 | 32k/1k/2.5k | 1E9588 | 16 | 2.7-5.5 | ISP/HVPP/JTAG | TQFP64/VQFN64 |

| ATmega32HVB | 32k/1k/2k | 1E9510 | 8 | 4.0-18.0 | ISP/HVPP/dW | TSSOP44 |

| ATmega32HVE ATmega32HVE2 | 32k/1k/4k | 1E9513 | 15 | 5.0-27.0 | ISP/HVSP/dW | TSOP28/LGA36 VQFN48 |

| ATmega48 ATmega48A ATmega48V | 4k/256/512 | 1E9205 | 20 20 10 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/dW | DIP28/TQFP32/VQFN28/VQFN32 DIP28/TQFP32/VQFN28/VQFN32/UFBGA32 DIP28/TQFP32/VQFN28/VQFN32 |

| ATmega48P ATmega48PA ATmega48PV | 4k/256/512 | 1E920A | 20 20 10 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/dW | DIP28/TQFP32/VQFN28/VQFN32 DIP28/TQFP32/VQFN28/VQFN32/UFBGA32 DIP28/TQFP32/VQFN28/VQFN32 |

| ATmega48PB | 4k/256/512 | 1E9210 | 20 | 1.8-5.5 | ISP/HVPP/dW | TQFP32/VQFN32 |

| ATmega64 ATmega64A ATmega64L | 64k/2k/4k | 1E9602 | 16 16 8 | 4.5-5.5 2.7-5.5 2.7-5.5 | ISP/HVPP/JTAG | TQFP64/VQFN64 |

| ATmega64C1 | 64k/2k/4k | 1E9686 | 16 | 2.7-5.5 | ISP/HVPP/dW | TQFP32/VQFN32 |

| ATmega64M1 | 64k/2k/4k | 1E9684 | 16 | 2.7-5.5 | ISP/HVPP/dW | TQFP32/VQFN32 |

| ATmega64HVE ATmega64HVE2 | 64k/1k/4k | 1E9610 | 15 | 5.0-27.0 | ISP/HVSP/dW | TSOP28/LGA36 VQFN48 |

| ATmega64RFR2 | 64k/2k/8k | 1EA602 | 16 | 1.8-3.6 | ISP/LVPP/JTAG | VQFN64 |

| ATmega88 ATmega88A ATmega88V | 8k/512/1k | 1E930A | 20 20 10 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/dW | DIP28/TQFP32/VQFN32 DIP28/TQFP32/VQFN28/VQFN32/UFBGA32 DIP28/TQFP32/VQFN32 |

| ATmega88P ATmega88PA ATmega88PV | 8k/512/1k | 1E930F | 20 20 10 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/dW | DIP28/TQFP32/VQFN32 DIP28/TQFP32/VQFN28/VQFN32/UFBGA32 DIP28/TQFP32/VQFN32 |

| ATmega88PB | 8k/512/1k | 1E9316 | 20 | 1.8-5.5 | ISP/HVPP/dW | TQFP32/VQFN32 |

| ATmega103 ATmega103L | 128k/4k/4k | 1E9701 | 6 4 | 4.0-5.5 2.7-3.6 | ISP/HVPP | TQFP64 |

| ATmega128 ATmega128A ATmega128L | 128k/4k/4k | 1E9702 | 16 16 8 | 4.5-5.5 2.7-5.5 2.7-5.5 | ISP/HVPP/JTAG | TQFP64/VQFN64 |

| ATmega128RFA1 | 128k/4k/16k | 1EA701 | 16 | 1.8-3.6 | ISP/LVPP/JTAG | VQFN64 |

| ATmega128RFR2 | 128k/4k/16k | 1EA702 | 16 | 1.8-3.6 | ISP/LVPP/JTAG | VQFN64 |

| ATmega161 ATmega161L | 16k/512/1k | 1E9401 | 8 4 | 4.0-5.5 2.7-5.5 | ISP/HVPP | DIP40/PLCC44/TQFP44 |

| ATmega162 ATmega162V | 16k/512/1k | 1E9404 | 16 8 | 2.7-5.5 1.8-5.5 | ISP/HVPP/JTAG | DIP40/TQFP44/VQFN44 |

| ATmega163 ATmega163L | 16k/512/1k | 1E9402 | 8 4 | 4.0-5.5 2.7-5.5 | ISP/HVPP | DIP40/TQFP44 |

| ATmega164 ATmega164A ATmega164V | 16k/512/1k | 1E940F | 20 20 10 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/JTAG | DIP40/TQFP44/VQFN44 DIP40/TQFP44/VQFN44/DRQFN44/VFBGA49 DIP40/TQFP44/VQFN44 |

| ATmega164P ATmega164PA ATmega164PV | 16k/512/1k | 1E940A | 20 20 10 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/JTAG | DIP40/TQFP44/VQFN44/DRQFN44 DIP40/TQFP44/VQFN44/DRQFN44/VFBGA49 DIP40/TQFP44/VQFN44 |

| ATmega165 ATmega165A ATmega165V | 16k/512/1k | 1E9405 1E9410 1E9405 | 16 16 8 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/JTAG | TQFP64/VQFN64 TQFP64/VQFN64/DRQFN64 TQFP64/VQFN64 |

| ATmega165P ATmega165PA ATmega165PV | 16k/512/1k | 1E9407 | 16 16 8 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/JTAG | TQFP64/VQFN64 TQFP64/VQFN64/DRQFN64 TQFP64/VQFN64 |

| ATmega168 ATmega168A ATmega168V | 16k/512/1k | 1E9406 | 20 20 10 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/dW | DIP28/TQFP32/VQFN32 DIP28/TQFP32/VQFN28/VQFN32/UFBGA32 DIP28/TQFP32/VQFN32 |

| ATmega168P ATmega168PA ATmega168PV | 16k/512/1k | 1E940B | 20 20 10 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/dW | DIP28/TQFP32/VQFN32 DIP28/TQFP32/QFN28/VQFN32/UFBGA32 DIP28/TQFP32/VQFN32 |

| ATmega168PB | 16k/512/1k | 1E9415 | 20 | 1.8-5.5 | ISP/HVPP/dW | TQFP32/VQFN32 |

| ATmega169 ATmega169A ATmega169V | 16k/512/1k | 1E9405 1E9411 1E9405 | 16 16 8 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/JTAG | TQFP64/VQFN64 TQFP64/VQFN64/DRQFN64 TQFP64/VQFN64 |

| ATmega169P ATmega169PA ATmega169PV | 16k/512/1k | 1E9405 | 16 16 8 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/JTAG | TQFP64/VQFN64/DRQFN64 |

| ATmega256RFR2 | 256k/8k/32k | 1EA802 | 16 | 1.8-3.6 | ISP/LVPP/JTAG | VQFN64 |

| ATmega323 ATmega323L | 32k/1k/2k | 1E9501 | 8 4 | 4.0-5.5 2.7-5.5 | ISP/HVPP/JTAG | DIP40/TQFP44 |

| ATmega324 ATmega324A ATmega324V | 32k/1k/2k | 1E9515 | 20 20 10 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/JTAG | DIP40/TQFP44/VQFN44 DIP40/TQFP44/VQFN44/DRQFN44/VFBGA49 DIP40/TQFP44/VQFN44 |

| ATmega324P ATmega324PA ATmega324PV | 32k/1k/2k | 1E9508 1E9511 1E9508 | 20 20 10 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/JTAG | DIP40/TQFP44/VQFN44 DIP40/TQFP44/VQFN44/DRQFN44/VFBGA49 DIP40/TQFP44/VQFN44 |

| ATmega324PB | 32k/1k/2k | 1E9517 | 20 | 1.8-5.5 | ISP/HVPP/JTAG | TQFP44/VQFN44 |

| ATmega325 ATmega325A ATmega325V | 32k/1k/2k | 1E9505 | 16 20 8 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/JTAG | TQFP64/VQFN64 |

| ATmega325P ATmega325PA ATmega325PV | 32k/1k/2k | 1E950D | 20 20 10 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/JTAG | TQFP64/VQFN64 |

| ATmega328 ATmega328P ATmega328PV | 32k/1k/2k | 1E9514 1E950F 1E950F | 20 20 10 | 1.8-5.5 2.7-5.5 1.8-5.5 | ISP/HVPP/dW | DIP28/TQFP32/VQFN28/VQFN32 DIP28/TQFP32/VQFN28/VQFN32 DIP28/TQFP32/VQFN32 |

| ATmega328PB | 32k/1k/2k | 1E9516 | 20 | 1.8-5.5 | ISP/HVPP/dW | TQFP32/VQFN32 |

| ATmega329 ATmega329A ATmega329V | 32k/1k/2k | 1E9503 | 16 20 8 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/JTAG | TQFP64/VQFN64 |

| ATmega329P ATmega329PA ATmega329PV | 32k/1k/2k | 1E950B | 20 20 10 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/JTAG | TQFP64/VQFN64 |

| ATmega406 | 40k/512/2k | 1E9507 | 1 | 4.0-25.0 | HVPP/JTAG | LQFP48 |

| ATmega603 ATmega603L | 64k/2k/4k | 1E9601 | 6 4 | 4.0-5.5 2.7-3.6 | ISP/HVPP | TQFP64 |

| ATmega640 ATmega640V | 64k/4k/8k | 1E9608 | 16 8 | 2.7-5.5 1.8-5.5 | ISP/HVPP/JTAG | TQFP100/TFBGA100/CBGA100 |

| ATmega644 ATmega644A ATmega644V | 64k/2k/4k | 1E9609 | 20 20 10 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/JTAG | DIP40/TQFP44/VQFN44 DIP40/TQFP44/VQFN44 DIP40/TQFP44/VQFN44 |

| ATmega644P ATmega644PA ATmega644PV | 64k/2k/4k | 1E960A | 20 20 10 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/JTAG | DIP40/TQFP44/VQFN44 |

| ATmega644RFR2 | 64k/2k/8k | 1EA603 | 16 | 1.8-3.6 | ISP/LVPP/JTAG | VQFN48 |

| ATmega645 ATmega645A ATmega645V | 64k/2k/4k | 1E9605 | 16 16 8 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/JTAG | TQFP64/VQFN64 |

| ATmega645P | 64k/2k/4k | 1E960D | 16 | 1.8-5.5 | ISP/HVPP/JTAG | TQFP64/VQFN64 |

| ATmega649 ATmega649A ATmega649V | 64k/2k/4k | 1E9603 | 16 16 8 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/JTAG | TQFP64/VQFN64 |

| ATmega649P | 64k/2k/4k | 1E960B | 16 | 1.8-5.5 | ISP/HVPP/JTAG | TQFP64/VQFN64 |

| ATmega1280 ATmega1280V | 128k/4k/8k | 1E9703 | 16 8 | 2.7-5.5 1.8-5.5 | ISP/HVPP/JTAG | TQFP100/TFBGA100/CBGA100 |

| ATmega1281 ATmega1281V | 128k/4k/8k | 1E9704 | 16 8 | 2.7-5.5 1.8-5.5 | ISP/HVPP/JTAG | TQFP64/VQFN64 |

| ATmega1284 ATmega1284P | 128k/4k/16k | 1E9706 1E9705 | 20 | 1.8-5.5 | ISP/HVPP/JTAG | DIP40/TQFP44/VQFN44 |

| ATmega1284RFR2 | 128k/4k/16k | 1EA703 | 16 | 1.8-3.6 | ISP/LVPP/JTAG | VQFN48 |

| ATmega2560 ATmega2560V | 256k/4k/8k | 1E9801 | 16 8 | 4.5-5.5 1.8-5.5 | ISP/HVPP/JTAG | TQFP100/TFBGA100/CBGA100 |

| ATmega2561 ATmega2561V | 256k/4k/8k | 1E9802 | 16 8 | 4.5-5.5 1.8-5.5 | ISP/HVPP/JTAG | TQFP64/VQFN64 |

| ATmega2564RFR2 Rev. A | 256k/8k/32k | 1EA803 1EA802 | 16 | 1.8-3.6 | ISP/LVPP/JTAG | VQFN48 |

| ATmega3250 ATmega3250A ATmega3250V | 32k/1k/2k | 1E9506 | 16 20 8 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/JTAG | TQFP100 |

| ATmega3250P ATmega3250PA ATmega3250PV | 32k/1k/2k | 1E950E | 20 20 10 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/JTAG | TQFP100 |

| ATmega3290 ATmega3290A ATmega3290V | 32k/1k/2k | 1E9504 | 16 20 8 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/JTAG | TQFP100 |

| ATmega3290P ATmega3290PA ATmega3290PV | 32k/1k/2k | 1E950C | 20 20 10 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/JTAG | TQFP100 |

| ATmega6450 ATmega6450A ATmega6450V | 64k/2k/4k | 1E9606 | 16 20 8 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/JTAG | TQFP100 |

| ATmega6450P | 64k/2k/4k | 1E960E | 20 | 1.8-5.5 | ISP/HVPP/JTAG | TQFP100 |

| ATmega6490 ATmega6490A ATmega6490V | 64k/2k/4k | 1E9604 | 16 20 8 | 2.7-5.5 1.8-5.5 1.8-5.5 | ISP/HVPP/JTAG | TQFP100 |

| ATmega6490P | 64k/2k/4k | 1E960C | 20 | 1.8-5.5 | ISP/HVPP/JTAG | TQFP100 |

| ATmega8515 ATmega8515L | 8k/512/512 | 1E9306 | 16 8 | 4.5-5.5 2.7-5.5 | ISP/HVPP | DIP40/PLCC44/TQFP44/VQFN44 |

| ATmega8535 ATmega8535L | 8k/512/512 | 1E9308 | 16 8 | 4.5-5.5 2.7-5.5 | ISP/HVPP | DIP40/PLCC44/TQFP44/VQFN44 |

| Model | FLASH/EEPR- OM/SRAM [B] | Sygnatura | Fmax [MHz] | Vcc [V] | Interfejs | Obudowa |

| ATtiny | ||||||

| ATtiny102 | 1k/-/32 | 1E900C | 12 | 1.8-5.5 | TPI | SOIC8/UDFN8 |

| ATtiny104 | 1k/-/32 | 1E900B | 12 | 1.8-5.5 | TPI | SOIC14 |

| ATtiny202 | 2k/64/128 | 1E9123 | 20 | 1.8-5.5 | UPDI | SOIC8 |

| ATtiny204 | 2k/64/128 | 1E9122 | 20 | 1.8-5.5 | UPDI | SOIC14 |

| ATtiny212 | 2k/64/128 | 1E9121 | 20 | 1.8-5.5 | UPDI | SOIC8 |

| ATtiny214 | 2k/64/128 | 1E9120 | 20 | 1.8-5.5 | UPDI | SOIC14 |

| ATtiny402 | 4k/128/256 | 1E9227 | 20 | 1.8-5.5 | UPDI | SOIC8 |

| ATtiny404 | 4k/128/256 | 1E9226 | 20 | 1.8-5.5 | UPDI | SOIC14 |

| ATtiny406 | 4k/128/256 | 1E9225 | 20 | 1.8-5.5 | UPDI | SOIC20/VQFN20 |

| ATtiny412 | 4k/128/256 | 1E9223 | 20 | 1.8-5.5 | UPDI | SOIC8 |

| ATtiny414 | 4k/128/256 | 1E9222 | 20 | 1.8-5.5 | UPDI | SOIC14 |

| ATtiny416 | 4k/128/256 | 1E9221 | 20 | 1.8-5.5 | UPDI | SOIC20/VQFN20 |

| ATtiny417 | 4k/128/256 | 1E9220 | 20 | 1.8-5.5 | UPDI | VQFN24 |

| ATtiny804 | 8k/128/512 | 1E9325 | 20 | 1.8-5.5 | UPDI | SOIC14 |

| ATtiny806 | 8k/128/512 | 1E9324 | 20 | 1.8-5.5 | UPDI | SOIC20/VQFN20 |

| ATtiny807 | 8k/128/512 | 1E9323 | 20 | 1.8-5.5 | UPDI | VQFN24 |

| ATtiny814 | 8k/128/512 | 1E9322 | 20 | 1.8-5.5 | UPDI | SOIC14 |

| ATtiny816 | 8k/128/512 | 1E9321 | 20 | 1.8-5.5 | UPDI | SOIC20/VQFN20 |

| ATtiny817 | 8k/128/512 | 1E9320 | 20 | 1.8-5.5 | UPDI | VQFN24 |

| ATtiny1604 | 16k/256/1k | 1E9425 | 20 | 1.8-5.5 | UPDI | SOIC14 |

| ATtiny1606 | 16k/256/1k | 1E9424 | 20 | 1.8-5.5 | UPDI | SOIC20/VQFN20 |

| ATtiny1607 | 16k/256/1k | 1E9423 | 20 | 1.8-5.5 | UPDI | VQFN24 |

| ATtiny1614 | 16k/256/2k | 1E9422 | 20 | 1.8-5.5 | UPDI | SOIC14 |

| ATtiny1616 | 16k/256/2k | 1E9421 | 20 | 1.8-5.5 | UPDI | SOIC20/VQFN20 |

| ATtiny1617 | 16k/256/2k | 1E9420 | 20 | 1.8-5.5 | UPDI | VQFN24 |

| ATtiny3214 | 32k/256/2k | 1E9520 | 20 | 1.8-5.5 | UPDI | SOIC14 |

| ATtiny3216 | 32k/256/2k | 1E9521 | 20 | 1.8-5.5 | UPDI | SOIC20/VQFN20 |

| ATtiny3217 | 32k/256/2k | 1E9522 | 20 | 1.8-5.5 | UPDI | VQFN24 |

| ATmega | ||||||

| ATmega808 | 8k/256/1k | 1E9326 | 20 | 1.8-5.5 | UPDI | SSOP28/TQFP32/VQFN32 |

| ATmega809 | 8k/256/1k | 1E932A | 20 | 1.8-5.5 | UPDI | TQFP48 |

| ATmega1608 | 16k/256/2k | 1E9427 | 20 | 1.8-5.5 | UPDI | SSOP28/TQFP32/VQFN32 |

| ATmega1609 | 16k/256/2k | 1E9426 | 20 | 1.8-5.5 | UPDI | TQFP48 |

| ATmega3208 | 32k/256/4k | 1E9530 | 20 | 1.8-5.5 | UPDI | SSOP28/TQFP32/VQFN32 |

| ATmega3209 | 32k/256/4k | 1E9531 | 20 | 1.8-5.5 | UPDI | TQFP48/UQFN48 |

| ATmega4808 | 48k/256/6k | 1E9650 | 20 | 1.8-5.5 | UPDI | SSOP28/TQFP32/VQFN32 |

| ATmega4809 | 48k/256/6k | 1E9651 | 20 | 1.8-5.5 | UPDI | DIP40/TQFP48/UQFN48 |

| ATxmega | ||||||

| ATxmega8E5 | 8k/512/1k | 1E9341 | 32 | 1.6-3.6 | PDI | TQFP32/VQFN32/UQFN32 |

| ATxmega16A4 ATxmega16A4U | 16k/1k/2k | 1E9441 | 32 | 1.6-3.6 | PDI | TQFP44/VQFN44/VFBGA49 |

| ATxmega16C4 | 16k/1k/2k | 1E9443 | 32 | 1.6-3.6 | PDI | TQFP44/VQFN44/VFBGA49 |

| ATxmega16D4 | 16k/1k/2k | 1E9442 | 32 | 1.6-3.6 | PDI | TQFP44/VQFN44/VFBGA49 |

| ATxmega16E5 | 16k/512/2k | 1E9445 | 32 | 1.6-3.6 | PDI | TQFP32/VQFN32/UQFN32 |

| ATxmega32A4 ATxmega32A4U | 32k/1k/4k | 1E9541 | 32 | 1.6-3.6 | PDI | TQFP44/VQFN44/VFBGA49 |

| ATxmega32C3 | 32k/1k/4k | 1E9549 | 32 | 1.6-3.6 | PDI | TQFP64/VQFN64 |

| ATxmega32C4 | 32k/1k/4k | 1E9544 | 32 | 1.6-3.6 | PDI | TQFP44/VQFN44/VFBGA49 |

| ATxmega32D3 | 32k/1k/4k | 1E954A | 32 | 1.6-3.6 | PDI | TQFP64/VQFN64 |

| ATxmega32D4 | 32k/1k/4k | 1E9542 | 32 | 1.6-3.6 | PDI | TQFP44/VQFN44/VFBGA49 |

| ATxmega32E5 | 32k/1k/4k | 1E954C | 32 | 1.6-3.6 | PDI | TQFP32/VQFN32/UQFN32 |

| ATxmega64A1 ATxmega64A1U | 64k/2k/4k | 1E964E | 32 | 1.6-3.6 | PDI/JTAG | TQFP100/TFBGA100/VFBGA100/CBGA100 |

| ATxmega64A3 ATxmega64A3U | 64k/2k/4k | 1E9642 | 32 | 1.6-3.6 | PDI/JTAG | TQFP64/VQFN64 |

| ATxmega64A4 ATxmega64A4U | 64k/2k/4k | 1E9646 | 32 | 1.6-3.6 | PDI | TQFP44/VQFN44 TQFP44/VQFN44/VFBGA49 |

| ATxmega64B1 | 64k/2k/4k | 1E9652 | 32 | 1.6-3.6 | PDI/JTAG | TQFP100/VFBGA100 |

| ATxmega64B3 | 64k/2k/4k | 1E9651 | 32 | 1.6-3.6 | PDI/JTAG | TQFP64/VQFN64 |

| ATxmega64C3 | 64k/2k/4k | 1E9649 | 32 | 1.6-3.6 | PDI | TQFP64/VQFN64 |

| ATxmega64D3 | 64k/2k/4k | 1E964A | 32 | 1.6-3.6 | PDI | TQFP64/VQFN64 |

| ATxmega64D4 | 64k/2k/4k | 1E9647 | 32 | 1.6-3.6 | PDI | TQFP44/VQFN44/VFBGA49 |

| ATxmega128A1 ATxmega128A1U | 128k/2k/8k | 1E974C | 32 | 1.6-3.6 | PDI/JTAG | TQFP100/TFBGA100/VFBGA100/CBGA100 |

| ATxmega128A3 ATxmega128A3U | 128k/2k/8k | 1E9742 | 32 | 1.6-3.6 | PDI/JTAG | TQFP64/VQFN64 |

| ATxmega128A4 ATxmega128A4U | 128k/2k/8k | 1E9746 | 32 | 1.6-3.6 | PDI | TQFP44/VQFN44 TQFP44/VQFN44/VFBGA49 |

| ATxmega128B1 | 128k/2k/8k | 1E974D | 32 | 1.6-3.6 | PDI/JTAG | TQFP100/VFBGA100 |

| ATxmega128B3 | 128k/2k/8k | 1E974B | 32 | 1.6-3.6 | PDI/JTAG | TQFP64/VQFN64 |

| ATxmega128C3 | 128k/2k/8k | 1E9752 | 32 | 1.6-3.6 | PDI | TQFP64/VQFN64 |

| ATxmega128D3 | 128k/2k/8k | 1E9748 | 32 | 1.6-3.6 | PDI | TQFP64/VQFN64 |

| ATxmega128D4 | 128k/2k/8k | 1E9747 | 32 | 1.6-3.6 | PDI | TQFP44/VQFN44/VFBGA49 |

| ATxmega192A1 | 192k/2k/16k | 1E974E | 32 | 1.6-3.6 | PDI/JTAG | TQFP100/CBGA100 |

| ATxmega192A3 ATxmega192A3U | 192k/2k/16k | 1E9744 | 32 | 1.6-3.6 | PDI/JTAG | TQFP64/VQFN64 |

| ATxmega192C3 | 192k/2k/16k | 1E9751 | 32 | 1.6-3.6 | PDI | TQFP64/VQFN64 |

| ATxmega192D3 | 192k/2k/16k | 1E9749 | 32 | 1.6-3.6 | PDI | TQFP64/VQFN64 |

| ATxmega256A1 | 256k/4k/16k | 1E9846 | 32 | 1.6-3.6 | PDI/JTAG | TQFP100/CBGA100 |

| ATxmega256A3 ATxmega256A3U | 256k/4k/16k | 1E9842 | 32 | 1.6-3.6 | PDI/JTAG | TQFP64/VQFN64 |

| ATxmega256A3B ATxmega256A3BU | 256k/4k/16k | 1E9843 | 32 | 1.6-3.6 | PDI/JTAG | TQFP64/VQFN64 |

| ATxmega256C3 | 256k/4k/16k | 1E9846 | 32 | 1.6-3.6 | PDI | TQFP64/VQFN64 |

| ATxmega256D3 | 256k/4k/16k | 1E9844 | 32 | 1.6-3.6 | PDI | TQFP64/VQFN64 |

| ATxmega384A1 ATxmega384C3 | 384k/4k/32k | 1E9845 | 32 | 1.6-3.6 | PDI/JTAG PDI | TQFP100/CBGA100 TQFP64/VQFN64 |

| ATxmega384D3 | 384k/4k/32k | 1E9847 | 32 | 1.6-3.6 | PDI | TQFP64/VQFN64 |