|

Wyjątki procesora MC68000 |

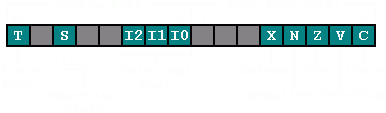

| "użytkownika" (User mode) - | w tym trybie procesor ma niższy poziom dostępu. Korzysta z oddzielnego stosu (wskaźnik A7=USP) i nie może wykonywać kilku instrukcji. Jeśli bit 13 ("S") rejestru SR jest zerem, to tryb "użytkownika" jest włączony. |

| "nadzorcy" (Supervisor mode) - | w tym trybie procesor ma wyższy poziom dostępu. Korzysta z oddzielnego stosu (wskaźnik A7=SSP) i może wykonywać wszystkie instrukcje. Jeśli bit 13 ("S") rejestru SR jest jedynką, to tryb "nadzorcy" jest włączony. |

| młodszy (użytkownika) - | rejestr kodów warunkowych CCR (Condition Code Register), który zawiera kody warunkowe ustawiane przez instrukcje. |

| starszy (systemowy) - | zawiera ustawienia procesora. Dostęp do niego w trybie "użytkownika" jest możliwy poprzez instrukcję "MOVE from SR", ale tylko na procesorze 68000. Na procesorze 68010/20/30/40/60 dostęp do tego bajtu jest możliwy tylko w trybie "nadzorcy". |

| Numer wektora (dziesiętnie) | Adres wektora (szesnastkowo) | Wyjątek |

| 0 1 | 0000 0004 | Reset: initial SSP Reset: initial PC |

| 2 | 0008 | Bus error |

| 3 | 000C | Address error |

| 4 | 0010 | Illegal instruction |

| 5 | 0014 | Zero divide |

| 6 | 0018 | CHK instruction |

| 7 | 001C | TRAPV instruction |

| 8 | 0020 | Privilege violation |

| 9 | 0024 | Trace |

| 10 | 0028 | Line 1010 emulator |

| 11 | 002C | Line 1111 emulator |

| 12...14 | 0030...0038 | Reserved (1) |

| 15 | 003C | Uninitialized interrupt |

| 16...23 | 0040...005C | Reserved (1) |

| 24 | 0060 | Spurious interrupt (2) |

| 25 | 0064 | Level 1 interrupt autovector |

| 26 | 0068 | Level 2 interrupt autovector |

| 27 | 006C | Level 3 interrupt autovector |

| 28 | 0070 | Level 4 interrupt autovector |

| 29 | 0074 | Level 5 interrupt autovector |

| 30 | 0078 | Level 6 interrupt autovector |

| 31 | 007C | Level 7 interrupt autovector |

| 32...47 | 0080...00BC | TRAP instruction (3) |

| 48...63 | 00C0...00FC | Reserved (1) |

| 64...255 | 0100...03FC | User interrupt (4) |

| GRUPA | WYJĄTEK | WYKONYWANIE |

| 0 | Reset Bus error Address error | w ciągu 2 cykli zegarowych |

| 1 | Trace Interrupt Illegal instruction Privilege violation | przed następną instrukcją |

| 2 | TRAP TRAPV CHK Zero divide | podczas wykonywania instrukcji |